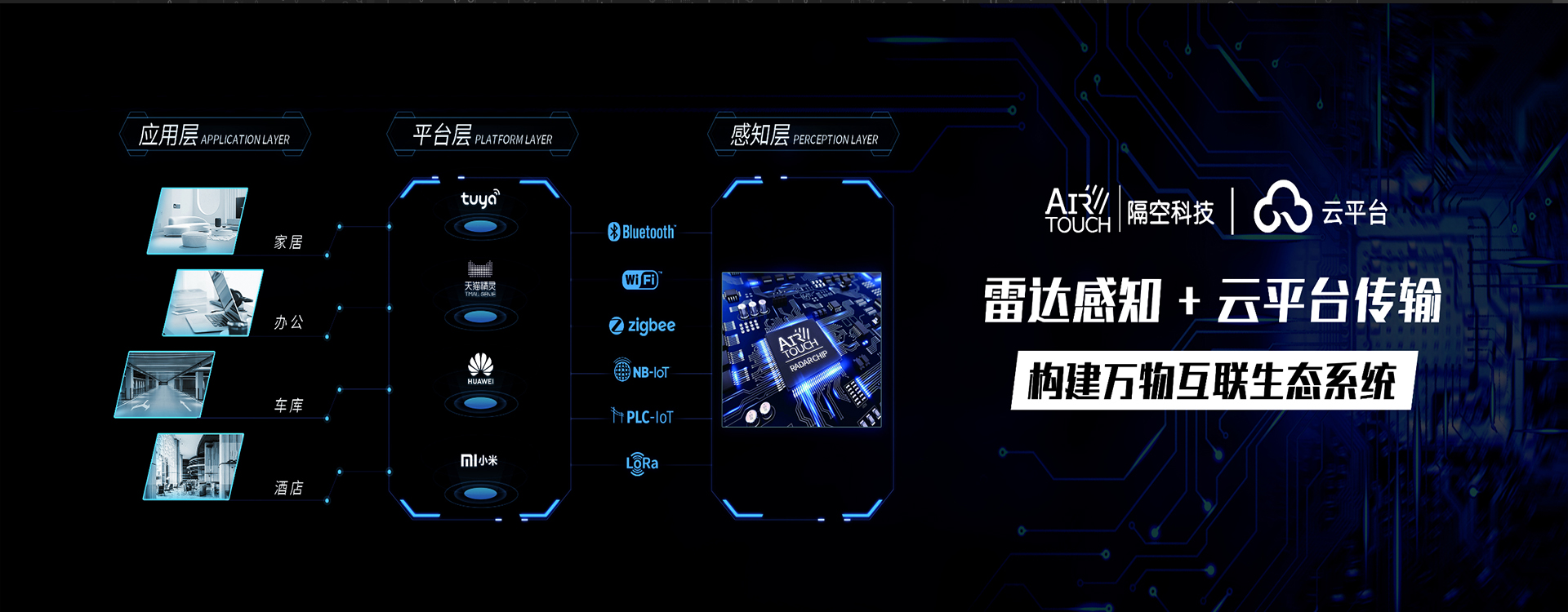

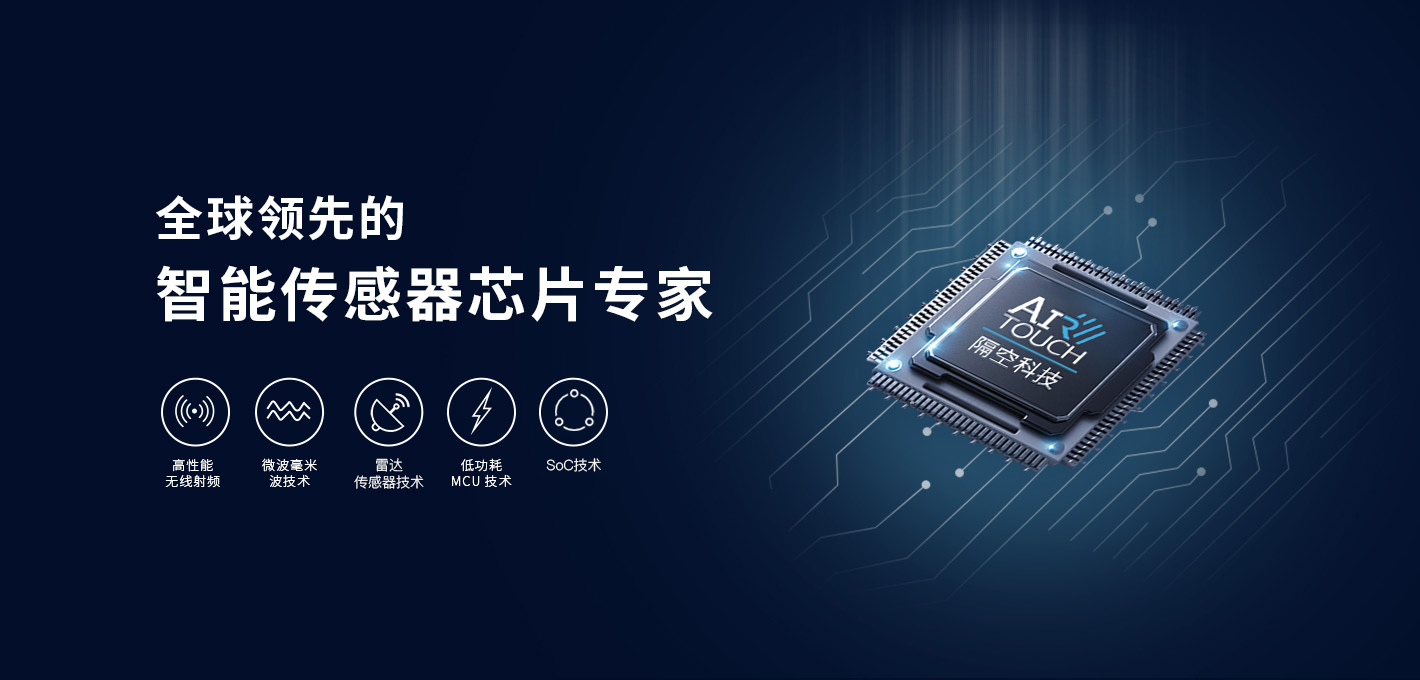

作为全球领先的智能传感器芯⽚专家,壹号平台注册链接_壹号平台下载安装专注于⾼性能⽆线射频技术、微波毫⽶波技术、雷达传感器技术、 低功耗MCU技术及SoC技术,定义并研发世界领先的“Me First” 芯⽚产品,提供⾼性价⽐的芯⽚、算法、软件及模组全套解决⽅案。

我们的产品

我们的核心优势

关于我们

作为全球领先的智能传感器芯⽚专家,壹号平台注册链接_壹号平台下载安装专注于⾼性能⽆线射频技术、微波毫⽶波技术、雷达传感器技术、 低功耗MCU技术及SoC技术,定义并研发世界领先的“Me First” 芯⽚产品,提供⾼性价⽐的芯⽚、算法、软件及模组全套解决⽅案。

我们的核心优势

新闻动态

公司动态

新品速递

展会活动

热招岗位

岗位职责:

1.集成电路版图设计、验证和优化。

岗位要求:

1.微电子学及相关理工科专业本科及以上学历;

2.熟悉CMOS工艺流程优先,具有扎实的半导体理论基础知识;

3.熟练掌握模拟电路版图设计工具及版图优化方法优先;

4.良好的团队合作精神,工作敬业负责;

5.良好的沟通能力,善于学习。